Data Sheet Issue:-1

# **Anode Shorted Gate Turn-Off Thyristor** Types G4000EF450

# **Absolute Maximum Ratings**

|                      | VOLTAGE RATINGS                                 | MAXIMUM<br>LIMITS | UNITS |

|----------------------|-------------------------------------------------|-------------------|-------|

| V <sub>DRM</sub>     | Repetitive peak off-state voltage, (note 1)     | 4500              | V     |

| V <sub>RSM</sub>     | Non-repetitive peak off-state voltage, (note 1) | 4500              | V     |

| $V_{\text{DC-link}}$ | Maximum continuous DC-link voltage              | 2800              | V     |

| V <sub>RRM</sub>     | Repetitive peak reverse voltage                 | 18                | V     |

| V <sub>RSM</sub>     | Non-repetitive peak reverse voltage             | 18                | V     |

|                     | RATINGS                                                          | MAXIMUM<br>LIMITS    | UNITS            |

|---------------------|------------------------------------------------------------------|----------------------|------------------|

| I <sub>TGQ</sub>    | Peak turn-off current, (note 2)                                  | 4000                 | А                |

| Ls                  | Snubber loop inductance, $I_{TM}=I_{TGQ}$ , (note 2)             | 200                  | nH               |

| I <sub>T(AV)M</sub> | Mean on-state current, T <sub>sink</sub> =55°C (note 3)          | 1530                 | А                |

| I <sub>T(RMS)</sub> | Nominal RMS on-state current, 25°C (note 3)                      | 3060                 | А                |

| I <sub>TSM</sub>    | Peak non-repetitive surge current t <sub>p</sub> =10ms, (Note 4) | 26.0                 | kA               |

| I <sub>TSM2</sub>   | Peak non-repetitive surge current t <sub>p</sub> =2ms, (Note 4)  | 32.6                 | kA               |

| l²t                 | I <sup>2</sup> t capacity for fusing t <sub>p</sub> =10ms        | 3.38×10 <sup>6</sup> | A <sup>2</sup> s |

| di/dt <sub>cr</sub> | Critical rate of rise of on-state current, (note 5)              | 500                  | A/µs             |

| P <sub>FGM</sub>    | Peak forward gate power                                          | 200                  | W                |

| P <sub>RGM</sub>    | Peak reverse gate power                                          | 25                   | kW               |

| I <sub>FGM</sub>    | Peak forward gate current                                        | 100                  | А                |

| V <sub>RGM</sub>    | Peak reverse gate voltage (note 6).                              | 18                   | V                |

| T <sub>j op</sub>   | Operating temperature range                                      | -40 to +125          | °C               |

| T <sub>stg</sub>    | Storage temperature range                                        | -40 to +125          | °C               |

Notes:-

1) V<sub>GK</sub>=-2Volts.

2) Tj=125°C, V\_D=2800V, V\_DM  $\leq$ 4500V digo/dt=40A/µs, I<sub>TGQ</sub>=4000A and Cs=6µF.

3) Double-side cooled, single phase; 50Hz, 180° half-sinewave. 4) T<sub>j</sub>((initial)=125°C, single phase, 180° sinewave, re-applied voltage V<sub>D</sub>=V<sub>R</sub>≤10V.

5) IT=4000A repetitive, IGM=50A, digm/dt=40A/µs. For di/dt>500A/µs please consult the factory.

6) May exceed this value during turn-off avalanche period.

# **Characteristics**

|                     | Parameter                                  | MIN  | TYP | MAX   | TEST CONDITIONS                                                                                                                                                     | UNITS |

|---------------------|--------------------------------------------|------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| V <sub>TM</sub>     | Maximum peak on-state voltage              | -    | 4.0 | 4.4   | I <sub>G</sub> =8A, I <sub>T</sub> =4000A                                                                                                                           | V     |

| IL.                 | Latching current                           | -    | 40  | 100   | Tj=25°C                                                                                                                                                             | А     |

| I <sub>H</sub>      | Holding current.                           | -    | 40  | 100   | Tj=25°C                                                                                                                                                             | А     |

| dv/dt <sub>cr</sub> | Critical rate of rise of off-state voltage | 1000 | -   | -     | V <sub>D</sub> =3000V, V <sub>GR</sub> =-2V                                                                                                                         | V/µs  |

| I <sub>DRM</sub>    | Peak off state current                     | -    | -   | 100   | Rated V <sub>DRM</sub> , V <sub>GR</sub> =-2V                                                                                                                       | mA    |

| I <sub>RRM</sub>    | Peak reverse current                       | -    | -   | 10    | V <sub>RR</sub> =18V                                                                                                                                                | mA    |

| I <sub>GKM</sub>    | Peak negative gate leakage current         | -    | -   | 10    | V <sub>GR</sub> =-18V                                                                                                                                               | mA    |

|                     | Gate trigger voltage                       | -    | 1.0 | -     | $T_j$ =-40°C<br>$T_j$ =25°C V <sub>D</sub> =25V, R <sub>L</sub> =25mΩ<br>$T_j$ =125°C                                                                               | V     |

| V <sub>GT</sub>     |                                            | -    | 0.8 | 1.5   |                                                                                                                                                                     | V     |

|                     |                                            | -    | 0.6 | -     |                                                                                                                                                                     | V     |

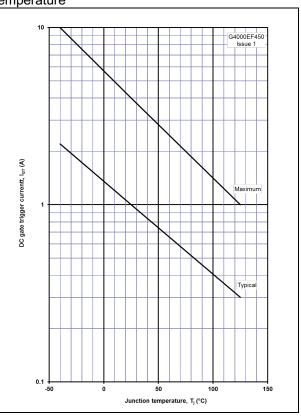

| I <sub>GT</sub>     | Gate trigger current                       | -    | 3.0 | 10    | $T_j$ =-40°C<br>$T_j$ =25°C V <sub>D</sub> =25V, R <sub>L</sub> =25mΩ                                                                                               | А     |

|                     |                                            | -    | 1.5 | 4     |                                                                                                                                                                     | А     |

|                     |                                            | 0.05 | 0.5 | 1     | Tj=125°C                                                                                                                                                            | А     |

| t <sub>d</sub>      | Delay time                                 | -    | 1.0 | 2     |                                                                                                                                                                     | μs    |

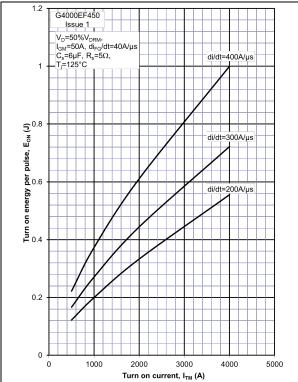

| t <sub>gt</sub>     | Turn-on time                               | -    | 3.5 | 7     | V <sub>D</sub> =2250V, I <sub>TGQ</sub> =4000A, di <sub>T</sub> /dt=400A/μs,<br>I <sub>GM</sub> =50A, di <sub>G</sub> /dt=40A/μs, C <sub>S</sub> =6μF, Rs=5Ω        | μs    |

| Eon                 | Turn-on energy                             | -    | 1   | 2.5   |                                                                                                                                                                     | J     |

| t <sub>f</sub>      | Fall time                                  | -    | 2.0 | -     |                                                                                                                                                                     | μs    |

| ts                  | Storage time                               | -    | 30  | 35    |                                                                                                                                                                     | μs    |

| t <sub>gq</sub>     | Turn-off time                              | -    | 32  | 40    |                                                                                                                                                                     | μs    |

| I <sub>GQM</sub>    | Peak turn-off gate current                 | -    | 875 | -     | V <sub>DM</sub> =3600V, V <sub>DM</sub> =80% V <sub>DRM</sub> , I <sub>TGQ</sub> =4000A,<br>di <sub>GQ</sub> /dt=40A/µs, V <sub>GR</sub> =-16V, C <sub>S</sub> =6µF | А     |

| Q <sub>GQ</sub>     | Turn-off gate charge                       | -    | 16  | -     |                                                                                                                                                                     | mC    |

| t <sub>tail</sub>   | Tail time                                  | -    | 20  | -     |                                                                                                                                                                     | μs    |

| E <sub>off</sub>    | Turn-off energy                            | -    | 10  | 15    |                                                                                                                                                                     | J     |

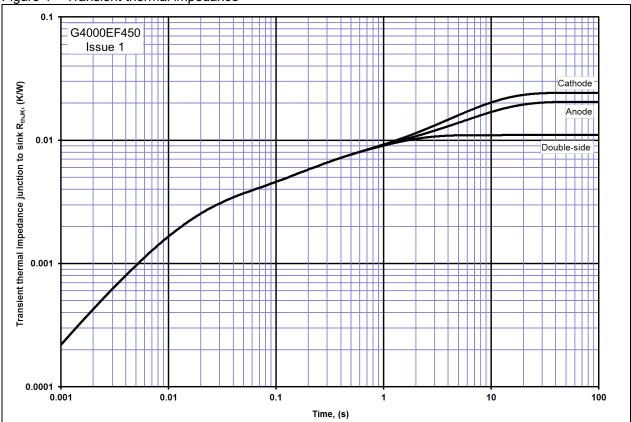

| R <sub>thJK</sub>   | Thermal resistance junction to sink        | -    | -   | 0.011 | Double side cooled                                                                                                                                                  | K/kW  |

|                     |                                            | -    | -   | 0.020 | Cathode side cooled                                                                                                                                                 | K/kW  |

|                     |                                            | -    | -   | 0.024 | Anode side cooled                                                                                                                                                   | K/kW  |

| F                   | Mounting force                             | 36   | -   | 48    | (see note 2)                                                                                                                                                        | kN    |

| Wt                  | Weight                                     | -    | 1.5 | -     |                                                                                                                                                                     | kg    |

Notes:-

Unless otherwise indicated T<sub>j</sub>=125°C.

For other clamping forces, consult factory.

### Notes on ratings and characteristics.

#### 1. Maximum Ratings.

1.1 Off-state voltage ratings.

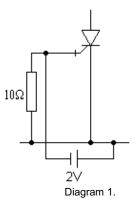

Unless otherwise indicated, all off-state voltage ratings are given for gate conditions as diagram 1. It should be noted that VDRM is the repeatable peak voltage, which may be applied to the device and does not relate to a DC operating condition.

## 1.2 Peak turn-off current.

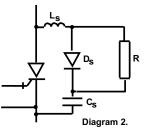

The figure given in maximum ratings is the highest value for normal operation of the device under conditions given in note 2 of ratings. A snubber circuit equivalent to that given in diagram 2 is assumed. If a more complex snubber, such as an Underland circuit, is employed then the equivalent  $C_s$  should be used and  $L_s$ <0.2µH must be ensured.

1.3 R.M.S and average current.

Measured as for standard thyristor conditions, double side cooled, single phase, 50Hz, 180° half-sinewave. These are included as a guide to compare the alternative types of GTO thyristors available; values cannot be applied to practical applications, as they do not include switching losses.

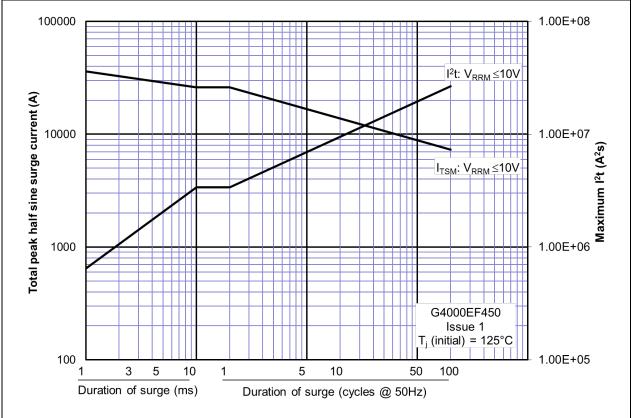

1.4 Surge rating and I<sup>2</sup>t.

Ratings are for half-sinewave, peak value against duration is given in the curve of figure 2.

## 1.5 Snubber loop inductance.

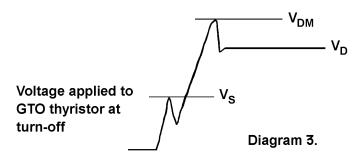

Use of GTO thyristors with snubber loop inductance,  $L_s$ <0.2µH implies no dangerous V<sub>s</sub> voltages (see diagrams 2 & 3) can be applied, provided the other conditions given in note 1.2 are enforced. Alternatively V<sub>s</sub> should be limited to 800 Volts to avoid possible device failure.

#### 1.6 Gate ratings

The absolute conditions above which the gate may be damaged. It is permitted to allow  $V_{GK(AV)}$  during turn-off to exceed  $V_{RGM}$  which is the implied DC condition.

## 2 Characteristics

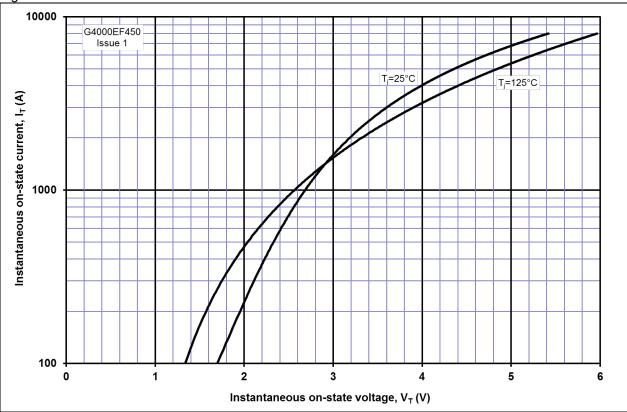

#### 2.1 Instantaneous on-state voltage

Measured using a 500µs square pulse, see also the curves of figure 1 for other values of ITM.

## 2.2 Latching and holding current

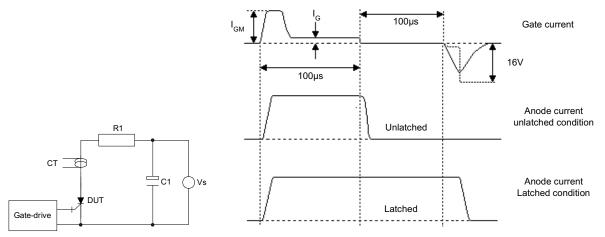

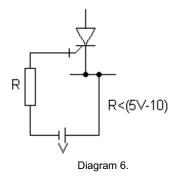

These are considered to be approximately equal and only the latching current is measured, type test only as outlined below. The test circuit and wave diagrams are given in diagram 4. The anode current is monitored on an oscilloscope while  $V_D$  is increased, until the current is seen to flow during the un-gated period between the end of  $I_G$  and the application of reverse gate voltage. Test frequency is 100Hz with  $I_{GM}$  &  $I_G$  as for  $t_d$  of characteristic data.

Diagram 4, Latching test circuit and waveforms.

#### 2.3 Critical dv/dt

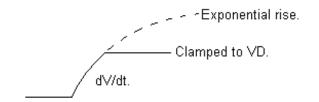

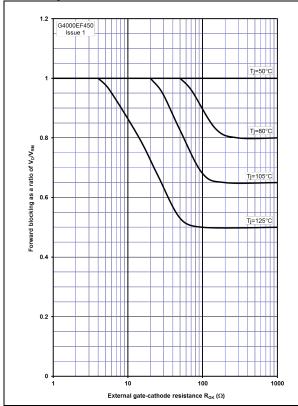

The gate conditions are the same as for 1.1, this characteristic is for off-state only and does not relate to dv/dt at turn-off. The measurement, type test only, is conducted using the exponential ramp method as shown in diagram 5. It should be noted that GTO thyristors have a poor static dv/dt capability if the gate is open circuit or  $R_{GK}$  is high impedance. Typical values: - dv/dt<100V/µs for  $R_{GK}$ >10 $\Omega$ .

2.4 Off-state leakage.

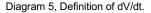

For IDRM see notes 1.1. For gate leakage IGK, the off-state gate circuit is required to sink this leakage and still maintain minimum of -2 Volts. See diagram 6.

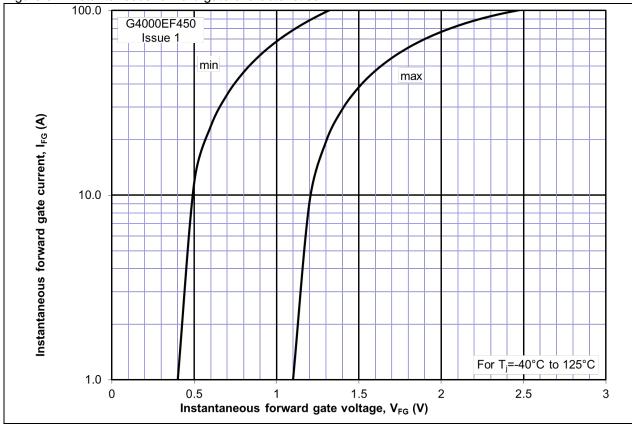

# 2.5 Gate trigger characteristics.

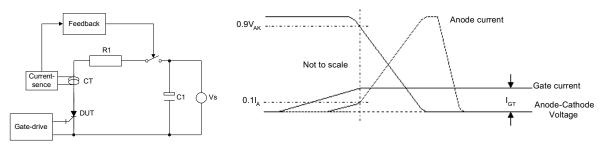

These are measured by slowly ramping up the gate current and monitoring the transition of anode current and voltage (see diagram 7). Maximum and typical data of gate trigger current, for the full junction temperature range, is given in the curves of figure 6. Only typical figures are given for gate trigger voltage for the full allowable junction temperature range. Figure 6 should be used when considering forward gate drive circuit requirement. The gate drive requirements should always be calculated for lowest junction temperature start-up condition.

Diagram 7, Gate trigger circuit and waveforms.

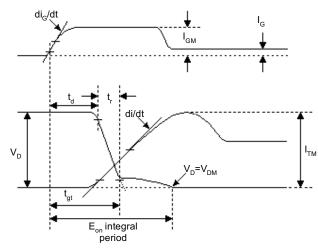

2.6 Turn-on characteristics The definitions of turn-on parameters used in the characteristic data are given in diagram 8.

Diagram 8, Turn-on wave-diagrams.

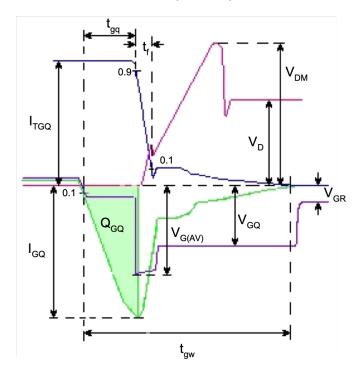

2.7 Turn-off characteristics The definitions of turn-off parameters used in the characteristic data are given in diagram 9.

Diagram 9, Turn-off parameter definitions.

# <u>Curves</u>

Figure 2 - Maximum surge and I<sup>2</sup>t Ratings

Figure 5 – Typical forward blocking voltage vs. external gate-cathode resistance

Figure 7 – Typical turn-on energy per pulse vs. turn-on current

Figure 6 – D.C. gate trigger current vs. junction temperature

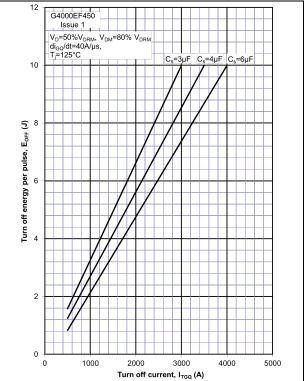

Figure 8 –Typical turn-off energy per pulse vs. turnoff current

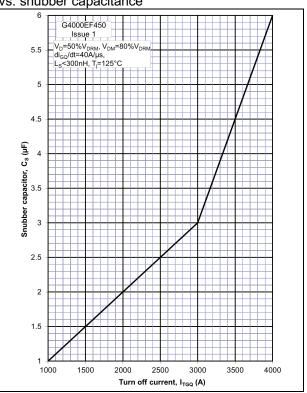

Figure 10 – Maximum permissible turn-off current vs. snubber capacitance

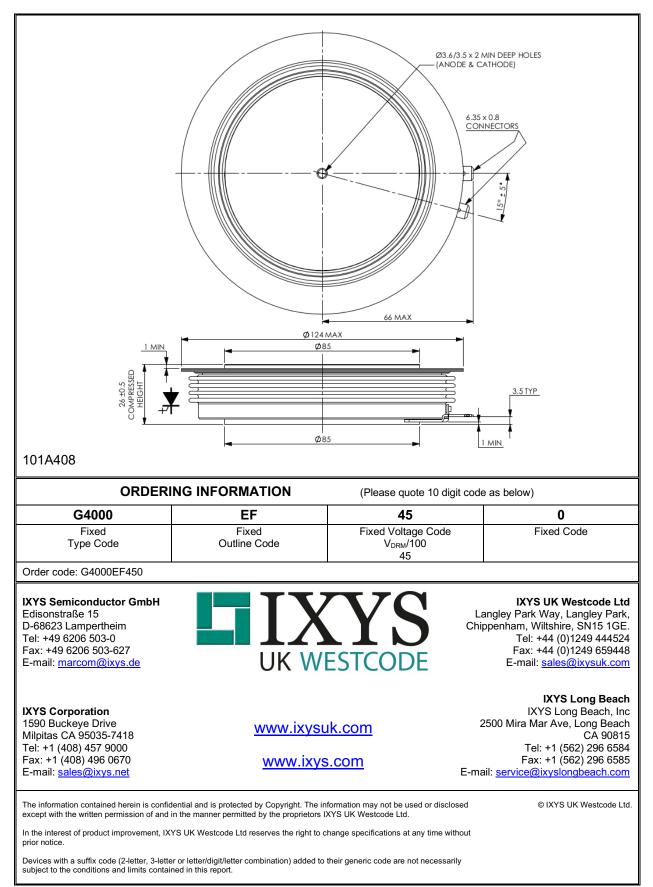

# **Outline Drawing & Ordering Information**

Disclaimer Notice - Information furnished is believed to be accurate and reliable. However, users should independently evaluate the suitability of and test each product selected for their own applications. Littelfuse products are not designed for, and may not be used in, all applications. Read complete Disclaimer Notice at www.littelfuse.com/disclaimer-electronics.